IVANIAC

Links

YouTube demo

World download

Architecture

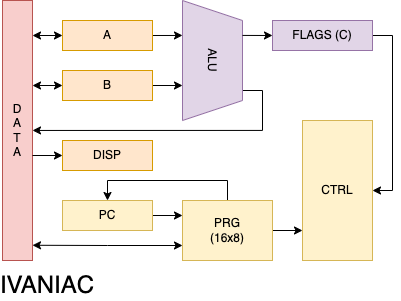

The IVANIAC is a Harvard architecture CPU, as it stores instructions in a separate instruction space from data. It lacks a dedicated data store, instead using two general-purpose registers. Both act as ALU operands, and can freely operate upon each other. It also features a display register, and a program counter

With a data width of 4 bits and no carry support, its numerical range is limited from 0 to 15.

The ALU can perform one of four functions on A and B— ADD, AND, OR, or XOR. Every operation sets the "overflow" flag, which is used by conditional jumps.

Instruction set

In total, the IVANIAC has 16 bytes of 8-bit-wide program memory. The first half of each byte is an opcode, and the last half can be an immediate value or address depending on the instruction.

- 00000000 - NOP

- 0001xxxx - MOV xxxx TO A

- 0010xxxx - MOV xxxx TO B

- 00110000 - MOV B TO A

- 01000000 - MOV A TO B

- 01010000 - ADD B TO A

- 01100000 - ADD A TO B

- 01110000 - AND B TO A

- 10000000 - XOR B TO A

- 10010000 - OR B TO A

- 10100000 - MOV INPUT TO A

- 10110000 - MOV INPUT TO B

- 11000000 - MOV A TO DISP

- 11010000 - MOV B TO DISP

- 1110xxxx - JMP TO xxxx

- 1111xxxx - JMP TO xxxx IF C != 1

In the demo uploaded to YouTube, the IVANIAC was shown calculating fibonacci numbers. The program alternated between adding A and B to each other, moving them to the display register, and performing a conditional jump if there was an overflow.

Background

In retrospect, the IVANIAC is a pretty poor design. Instruction decoding relies on slow repeaters, there's no arithmetic carry, no data memory, and address space is severely limited with 4 bits. However, I'm still proud of having built it.

I began working on the machine in late 2019, as a high school sophomore. I knew relatively little about computer engineering, but had nevertheless wanted to build a redstone CPU. Far in over my head, the project quickly fizzled out. By the time April 2020 came around, I was stuck at home and had nothing better to do but finish the IVANIAC. After an entire week of building, it was finally completed.

It's amazing that the IVANIAC works at all, considering I didn't have any clear plans or schematics. I came up with everything as I went along, learning CPU design for the first time. Despite its inherent quirks, I'll always champion the IVANIAC as my first-ever architecture.